在刚刚于旧金山结束的半导体技术大会SEMICON West上,英特尔发布了Co-EMIB、ODI、MDIO三种封装,互连及接口技术,用来解决不同规格芯片(Die)在水平和垂直维度上的互连及电气问题。而这些互连和电气问题正是限制芯片自由堆叠的关键因素。

为何要将芯片进行堆叠?

要构建一个标准的计算机,除了要有传统意义的CPU之外,主板上还要安装内存、芯片组、各类I/O芯片等等。一块能够实现标准计算机功能的电路板上除了上述的各类芯片之外还需要留出大量的空间来完成供电、滤波和互连布线工作。因此,想要实现完整的计算机功能,PCB板还是需要有一定体积的。而这一体积通常也会随着计算机性能的提升和扩展性的增大而增大。

虽然这种情况对于传统桌面PC、数据中心等应用场景来说无伤大雅,但对于很多新兴的物联网、边缘计算场景来说,体积的限制确实非常致命的。而在现实生活中,我们更是经常会受到这些问题的困扰。

例如,我们总是抱怨的手机电池问题在很大程度上就是因为电路板太大,而留给电池的空间太小;智能手环、手表的电池问题也是同样的原因。而那些奇形怪状的智能设备之所以会被设计成这样,多半也是在想尽办法为电路板和电池的安装腾出足够的空间。

在过去,解决这一问题的思路除了提升半导体制程技术之外就是把更多功能塞进同一块芯片里,形成所谓的SoC(System on a Chip)。但在践行这一思路的过程中,随着芯片功能的增加和体积的增大,芯片设计、测试和制造的难度正在成几何倍数增加。这在提高产品成本的同时也会严重拖慢新产品上市的速度。为了解决这一困扰行业良久的问题,芯片的3D堆叠概念被提了出来。

芯片,不仅要“堆”,还要“叠”

乐高积木不仅是很多小朋友的玩具,更是很多大孩子的休闲爱好。它最大的魅力就在于通过小方块的横纵交错构建万事万物。就像上帝只用几个基本粒子就构建出丰富多彩的宇宙一样;在横纵交错的堆叠里,限制我们的只有想象力而已。

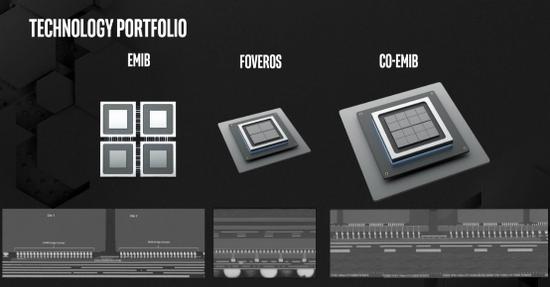

2018年12月,英特尔首次对外展示了逻辑芯片(也就是计算芯片)的3D堆叠封装方案——Foveros。通过在水平布置的芯片之上垂直安置更多面积更小、功能更简单的小芯片来让方案整体具备更完整的功能。

例如我们可以在CPU之上堆叠各类小型的IO控制芯片,从而制造出兼备计算与IO功能的产品;或者,我们可以干脆将芯片组(南桥)与各种Type-C、蓝牙、WiFi等控制芯片堆叠在一起,制造出超高整合度的控制芯片。

当然,除了功能性的提升之外,Foveros技术对于产业来说最迷人的地方在于他可以将过去漫长的重新设计、测试、流片过程统统省去,直接将不同厂牌、不同IP、不同工艺的各种成熟方案封装在一起,从而大幅降低成本并提升产品上市速度。同时,这种整合程度的提升也能够进一步缩小整体方案的体积,为万事万物的智能化、物联网化打开全新的大门。

如果只是将不同的芯片在垂直方向上叠在一起,那么故事就应该到此完结了。但英特尔从来不是小富即安的人,英特尔想要做的是让芯片在水平和垂直方向上都获得延展。因此,才有了我们今天要讲的主角——Co-EMIB、ODI、MDIO。

芯片堆叠,互连是关键

其实,与在PCB上布线类似,想要在同一块基板上实现水平和垂直方向上的多芯片堆叠,除了芯片本身之外,最大的挑战来自于解决芯片的供电以及他们之间的数据互联问题。

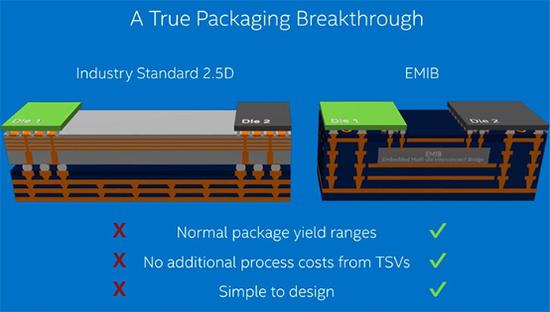

在2018年的HotChip大会上,英特尔发布了自己的芯片EMIB芯片封装技术,该技术允许在同一基板上将多颗芯片进行水平方向上的布置时能够获得比原先的MCP多芯片封装技术更高的芯片互连效率。相对于其他公司的2.5D封装,EMIB将原本需要额外加入的互连层进行了整合,让水平放置的芯片能够在同一个物理层中实现供电、互连。

而在本次的SEMICON West大会上,英特尔则发布了EMIB的升级版——Co-EMIB技术,在EMIB水平互联的基础之上实现了Foveros 3D堆叠芯片之间的水平互联(当然,仍旧是在同一块基板上的),从而让不同芯片堆叠之间都能够实现高效的数据交换。技术原理视频:https://v.qq.com/x/page/c0896qqnn45.html

而为了进一步提高水平与垂直堆叠的灵活性,英特尔还推出了一个额外的物理互连层技术——ODI。他存在于基板与芯片之间,在这一层上,英特尔可以通过远远大于传统封装技术的密度来进行埋线和布置连接针脚。从而在保证芯片供电的情况下实现更高的互联带宽。ODI技术分为两种,分别对应单芯片和多芯片的互连。技术原理视频:https://v.qq.com/x/page/z0896fleu3r.html

更进一步的,英特尔还发布了全新 MDIO技术。简单地说,MDIO是一种性能更好的芯片到芯片之间的接口(引脚)技术。相对于之前英特尔所使用的AIB(高级接口总线)技术,MDIO能够在更小的连接面积内实现更高的数据带宽。这样,即便是使用ODI技术中更细的针脚也能够满足芯片之间数据带宽的需求。

通过在连接方式、连接层、连接引脚等影响芯片堆叠的细节上的全面技术革新,英特尔终于实现了在单一基板上以水平和垂直方式封装更多芯片(Die)的愿景。

正如同乐高积木一样,在打通互联障碍之后,通过水平和垂直方向上的不同芯片堆叠,我们终于可以方寸之间实现更大的梦想。现在,限制我们的或许真的只有想象力了。

英特尔的新未来

英特尔围绕自身在半导体技术和相关应用方面的能力构建了支撑自身“以数据为中心”战略的六大技术支柱。提出了以制程和封装、架构、内存和存储、互连、安全、软件这六大技术支柱来应对未来数据量的爆炸式增长、数据的多样化以及处理方式的多样性。而封装技术毫无疑问也是这在这六大技术支柱中的重要一环。

在10nm工艺全面蓄势待发的当下,英特尔如果能够在封装技术方面突破水平与垂直方向的限制,那么等待英特尔和我们的将是一个全新的世界。

解决一个小问题并不难,但解决由无数小问题组合而成的大问题却非常复杂。这个道理在半导体行业同样适用。设计单一功能的芯片相对简单,但要在满足性能、功耗等需求的情况下将各种功能集合在一起,那么这将是一项极其浩大的工程。

通过将现有的各种成熟方案进行简单的堆叠,我们便能够制造出功能更完整的单封装芯片,用一套供电和IO设计完成整个系统,从而把方案设计的更小、更简单、更高效。而达成这一切所需的时间和成本也会更低。这便是英特尔3D封装技术的意义所在。这对于所有产业以及整个社会来说都是一个巨大的机会。

而之于英特尔,堆叠这种全新的半导体设计生产方式也有望将行业内部的竞争推向全新的维度,一个再次以英特尔技术为主力方向的维度。

当芯片成为乐高积木,一个以计算为基础、以数据为中心的多元化计算未来便不再遥远。

后记:

在数据中心之外,计算设备的体积、功耗和功能是万物互联和智能时代的主要挑战之一;而在数据中心之内,不同类型数据的大量出现却也让计算架构再次面临分裂的困境(代表现象就是Training和Inference领域中的异构计算的崛起);而这种分裂会对数据中心的管理和运维带来巨大挑战。而半导体晶片堆叠技术的出现则让英特尔看到了从战略上看到机会。

通过将不同功能、不同IP的晶片封装在一起,数据中心在未来有望大幅度简化架构,将计算类型的分裂严格限制在芯片内部,从而在更大的层面上实现统一。这就完美解决了计算架构分裂所带来的管理及运维挑战。

当然,从另一方面来说,将计算与各类功能型晶片在物理上拉近距离也有助于实现更高的整体性能,从而缓解数据量暴涨所带来的处理压力,让现有计算机架构和数据中心结构能够在更长一段时间内满足实际需求。

虽然英特尔在SEMICON West上发布的技术目前还没有全面推广应用,但英特尔已经在Agilex FPGA上使用了EMIB技术,从而实现了更高的集成度和更好的整体性能(112Gb/s的数据吞吐量,目前行业无出其右)。而这也从侧面证明了这一技术在目前技术条件下的应用前景。

因此,还是套用那句老话:半导体晶片的3D堆叠是一盘很大的棋,更是一场需要持续投入的马拉松。